## **Brain-Computer Interface SoC with High-Throughput Neural Signal Processing Unit**

Wooseok Byun<sup>1</sup>, Hyunji Kim<sup>2</sup>, Sunyoung Park<sup>2</sup> and Ji-Hoon Kim<sup>2</sup> **KAIST<sup>1</sup>**, Ewha Womans University<sup>2</sup>

Introduction

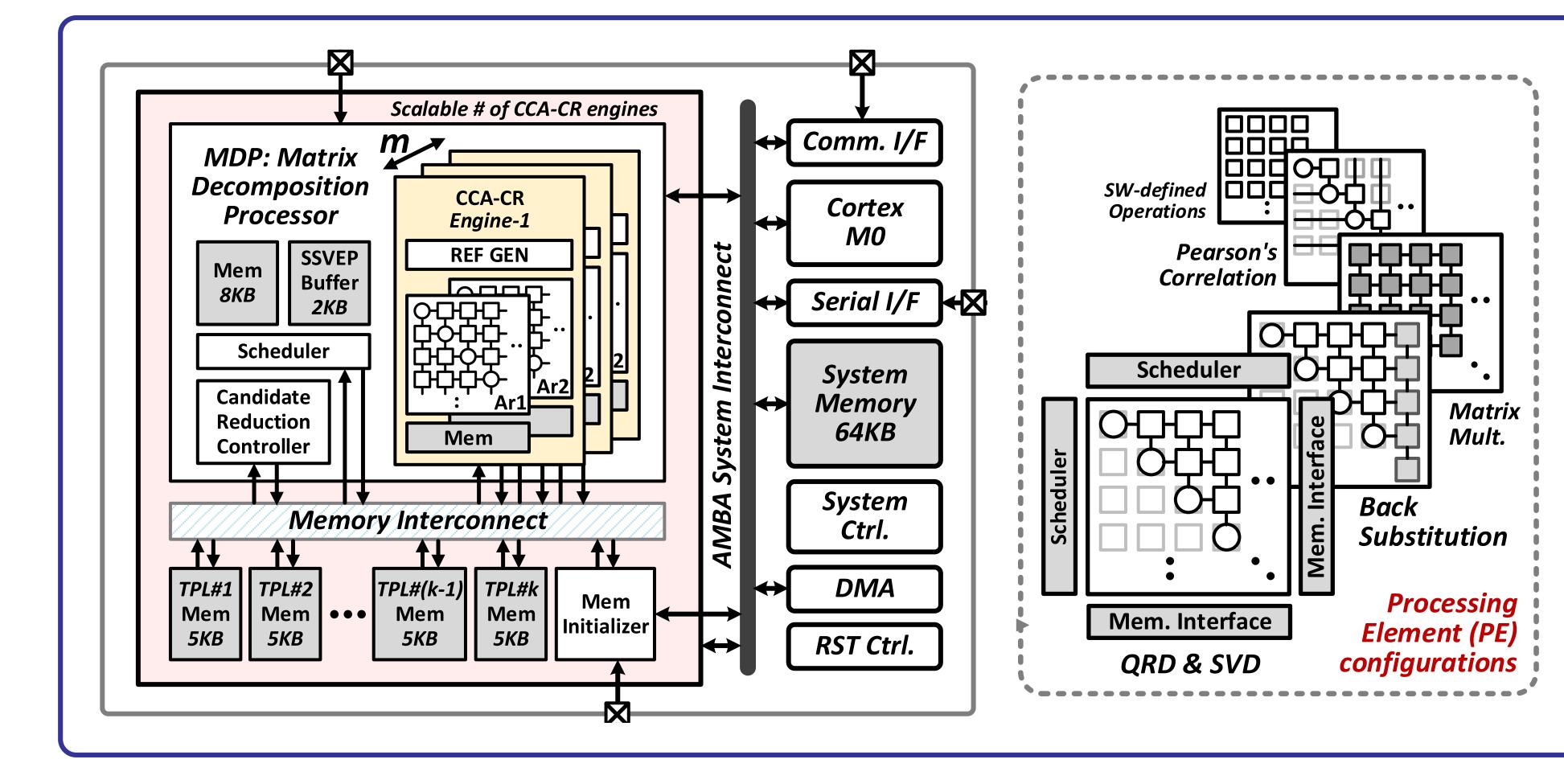

Steady-state visual evoked potential (SSVEP) based wearable brain-computer interface (BCI) have been widely studied enable paralyzed patients to communicate with others. However, target identification accuracy and information transfer rate (ITR), which are general performance indicators of SSVEP-based BCI system, still need to be further improved in wearable devices. In this work, we propose 8-channel SSVEP-based visual target identification system-onprocessing load by at least 75% without degrading target identification accuracy and ITR. This paper also proposes based CCA-CR engines. The proposed chip was fabricated in 65nm CMOS technology and operates at 50MHz 1.2V.

chip (SoC) to improve the ITR for low-cost wearable BCI device while reducing the computational complexity dramatically without accuracy degradation. The proposed target identification algorithm, CCA-CR based on canonical correlation analysis (CCA), includes algorithmic optimizations and candidate reduction (CR) method to reduce the signal matrix decomposition processor (MDP) that computes complex matrix arithmetic operations through systolic array

## **PROPOSED ARCHITECTURE**

Implementation of proposed CCA-**CR acceleration architecture:** candidate reduction (CR) based optimized CCA-Comb algorithm was proposed and implemented through suitable microarchitecture with 3 **CCA-CR engines (each has 2 arrays)**

**Digit-Serial Arithmetic PE: each PE** (processing element) performs 4-bit digit serial arithmetic for low area

## **CHIP IMPLEMENTATION AND RESULTS**

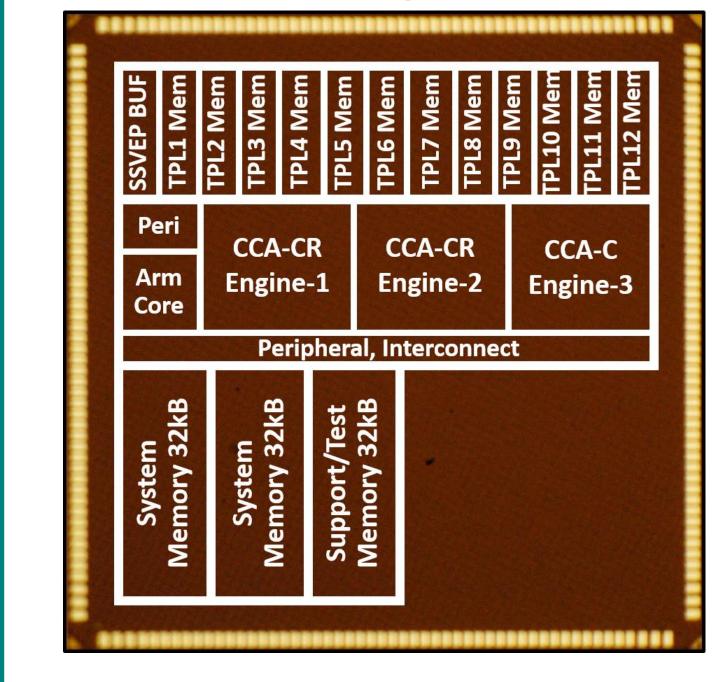

## **Die Micrograph** 63

- Die size: 4x4mm<sup>2</sup>

- **3 engines (6 arrays)**

- **8x8 PE array** 23

- Area optimized arch.

- **Digit serial ALU in PE**

- **12 memory banks**

| Chip Implementation                         |  |

|---------------------------------------------|--|

| Chip Information                            |  |

| 65nm CMOS                                   |  |

| 50 MHz, 1.2V(core), 3.5x3.5 mm <sup>2</sup> |  |

|                                             |  |

for subject-specific **EEG template data** of 12 visual targets

| Circuit Type          | Digital (Cell-based) Design |

|-----------------------|-----------------------------|

| <b>On-Chip Memory</b> | 158kB                       |

|                       |                             |

This work proposes 8-channel SSVEP target identification SoC with CCA-CR, which reduces the number of CCA-Comb calculations by 75% without degrading target identification accuracy and ITR. Thanks to the multi-channel SSVEP, the SSVEP recording time is short, resulting in a significantly reduced target identification latency and a 63% increase in ITR.

This chip fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.